[最も好ましい] Verilog Ifdef Or Condition 643764-Verilog Ifdef Conditional

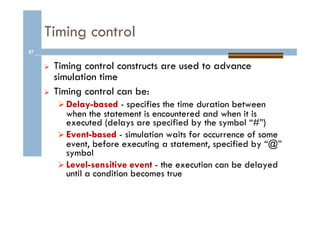

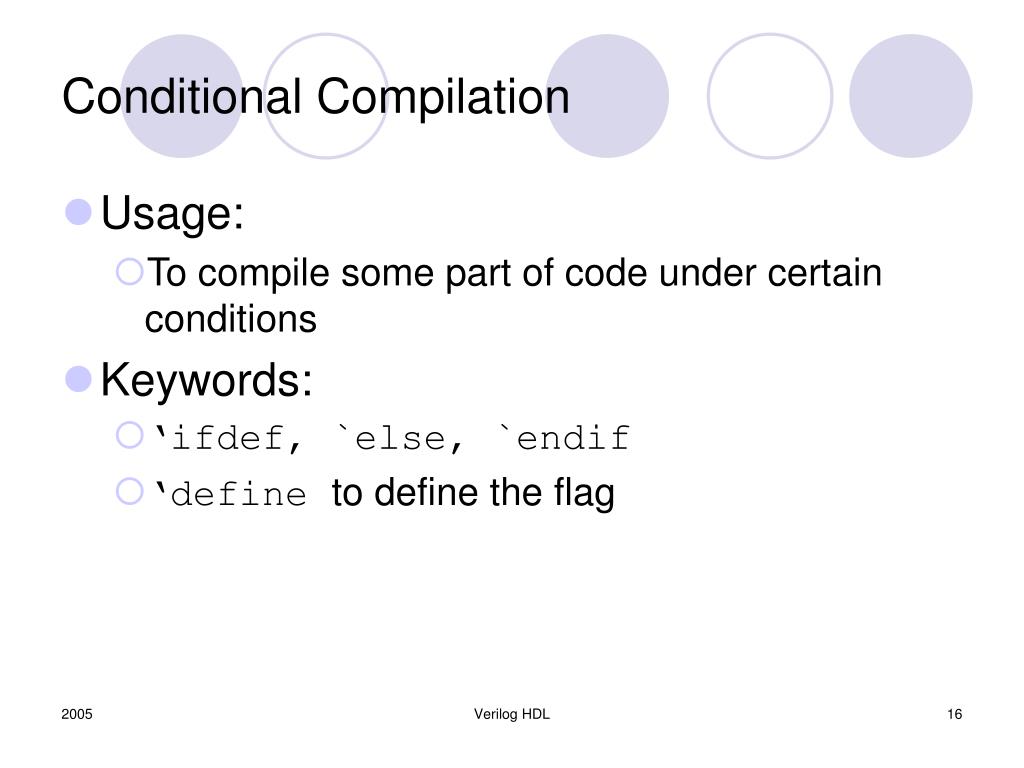

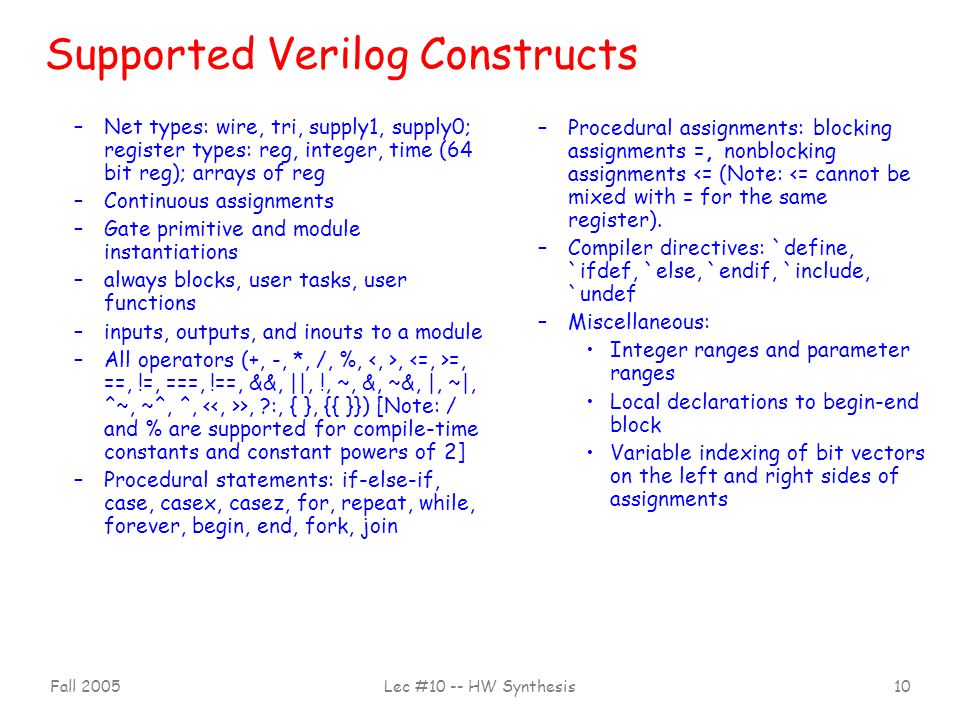

Web33 Data types¶ Data types can be divided into two groups as follows, Net group Net group represents the physical connection between components eg wire, wand and wor etcIn the tutorials, we will use only one net data type ie ‘wire’,WebVerilog `ifdef Conditional Compilation // Style #1 Only single `ifdef `ifdef // Statements `endif // Style #2 `ifdef with `else part `ifdef // Statements `else //Web or #if defined (LINUX) defined (ANDROID) // your code here #endif /* LINUX ANDROID */ Both above are the same, which one you use simply depends on your taste

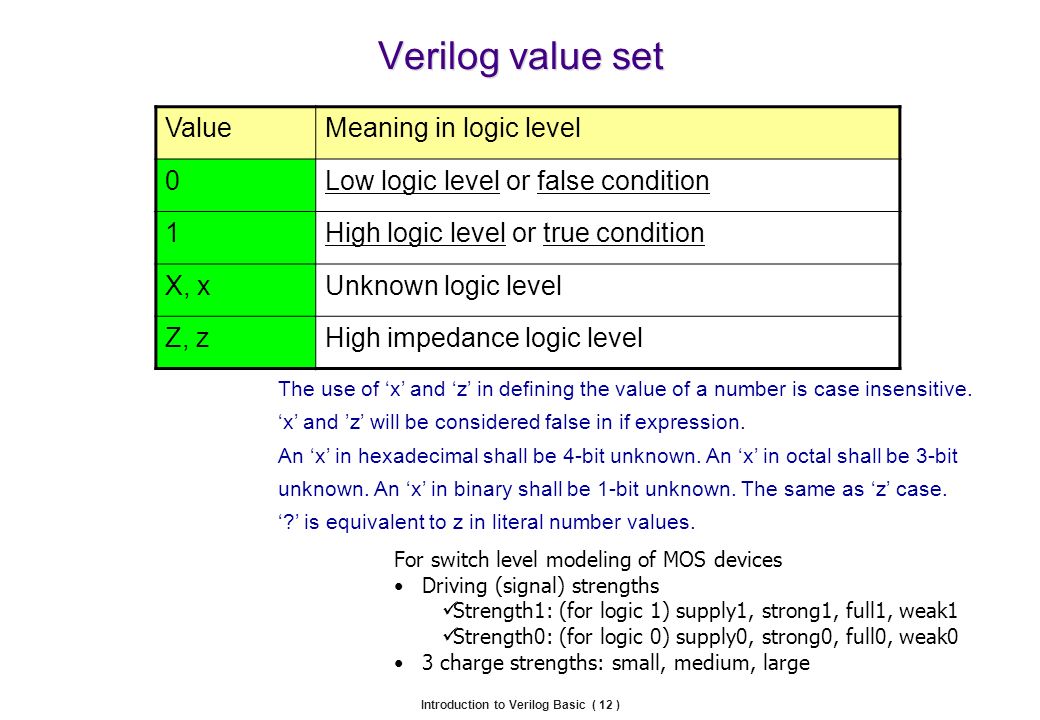

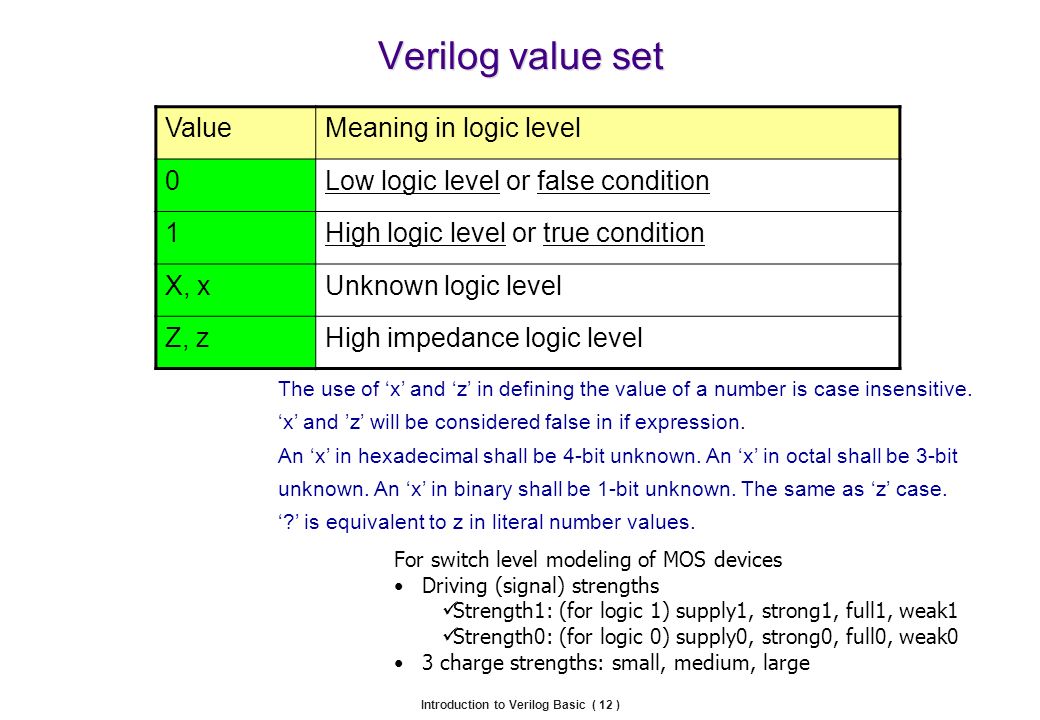

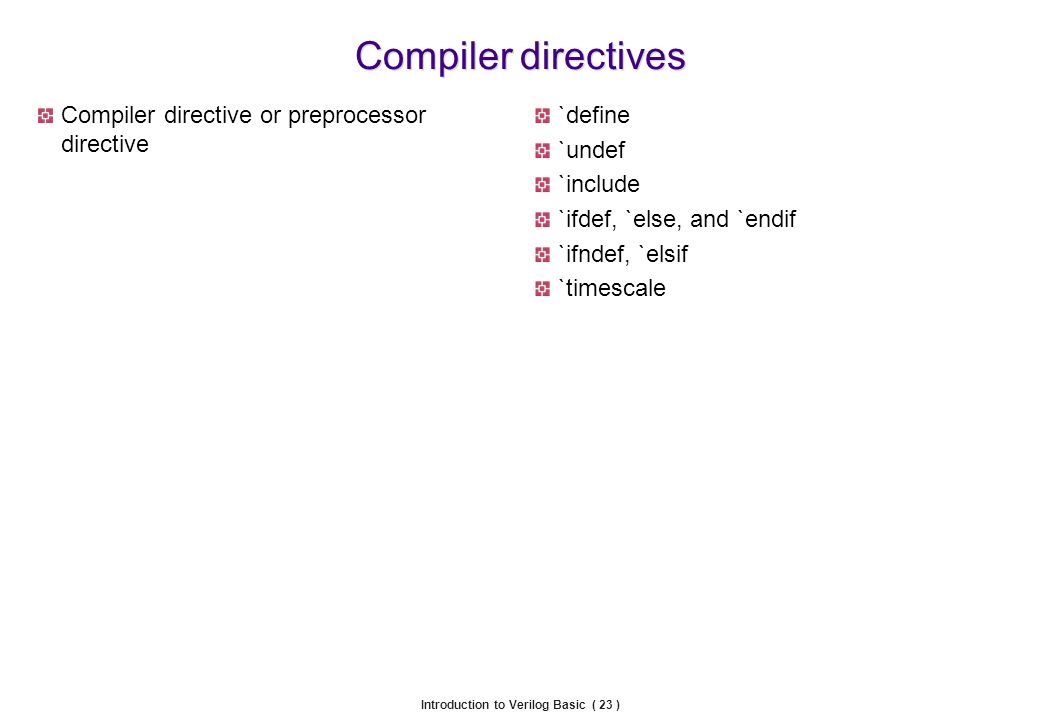

Verilog Basic Language Constructs Lexical Convention Data Types And So On Spring Ppt Download

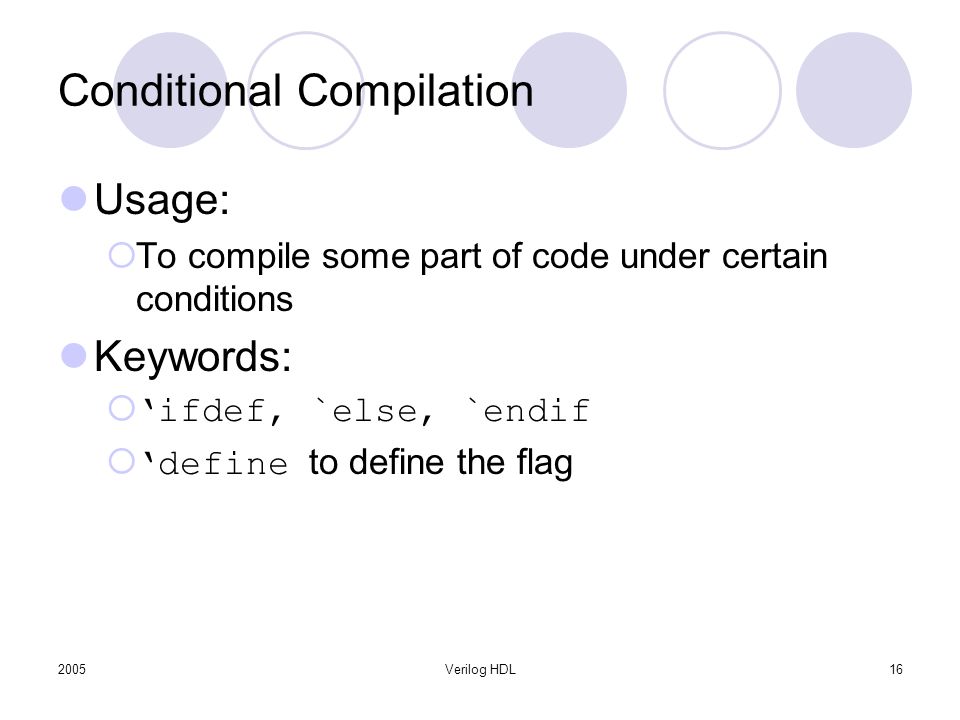

Verilog ifdef conditional

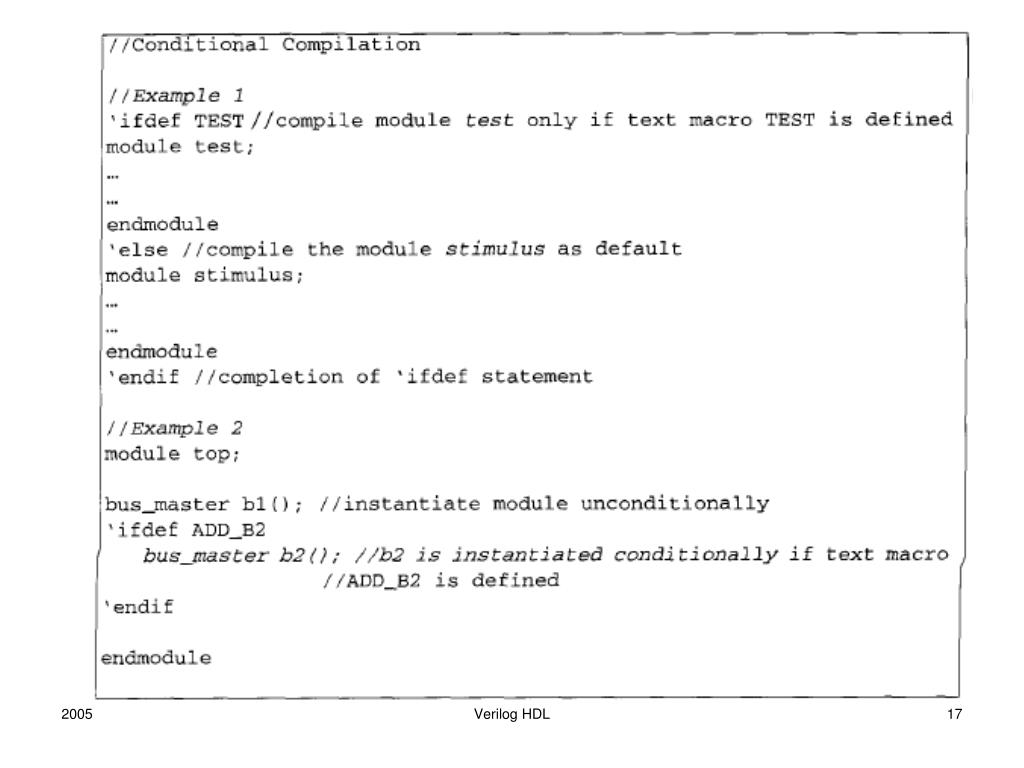

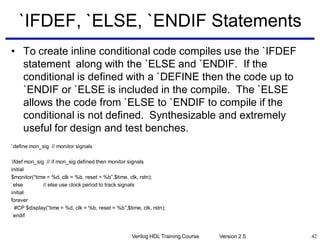

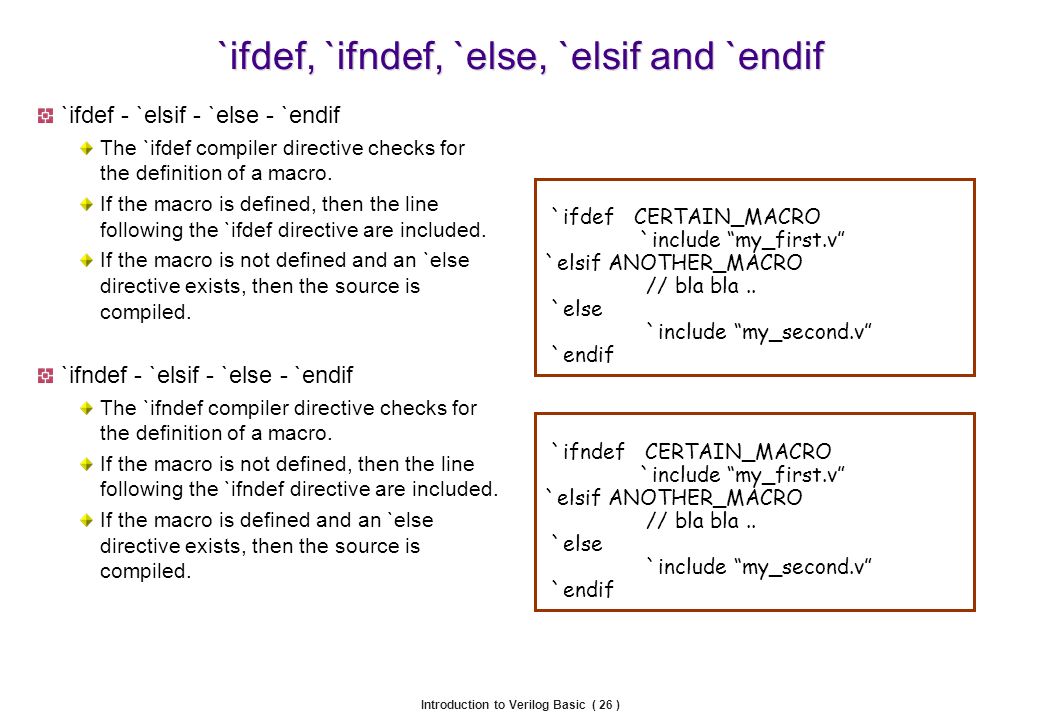

Verilog ifdef conditional-WebThese directives can be used to decide which lines of Verilog code should be included for the compilation (Example 4) The `ifdef directive checks if a macro name that follows thisWebThe #elseif, #else, and #endif directives are valid only following a #ifdef directive If the #ifdef directive evaluated to be true, t hen these directives ( #elseif, #else, and #endif ) stop

Verilog Tutorial 3 Define Text Macros Youtube

WebYour UVM, SystemVerilog and Coverage related questions by a preprocessor before the compiler sees the code code if!WebIn a compile, once QII sees a `define, it will be visible to all Verilog source files that are analyzed (parsed) later This is actually a rather nasty behavior that's defined by the IEEEOtherwise, the textiffalse, if any, is effectiveThe rules for expansion and testing of variablename are identical to the ifdef directive Extra spaces are allowed and ignored at the beginning of the conditional directive line, but a tab is not

`endif `ifdef HALF_RATE or QURD_RATE $display("I am in else part");Web In simpler words, using these statements, the execution of specific code lines can be controlled using some conditions Verilog provides two types of conditionalWebThe if statetement in verilog is very similar to the if statements in other programming languages We will now write a combinatorial verilog example that make use of if statement

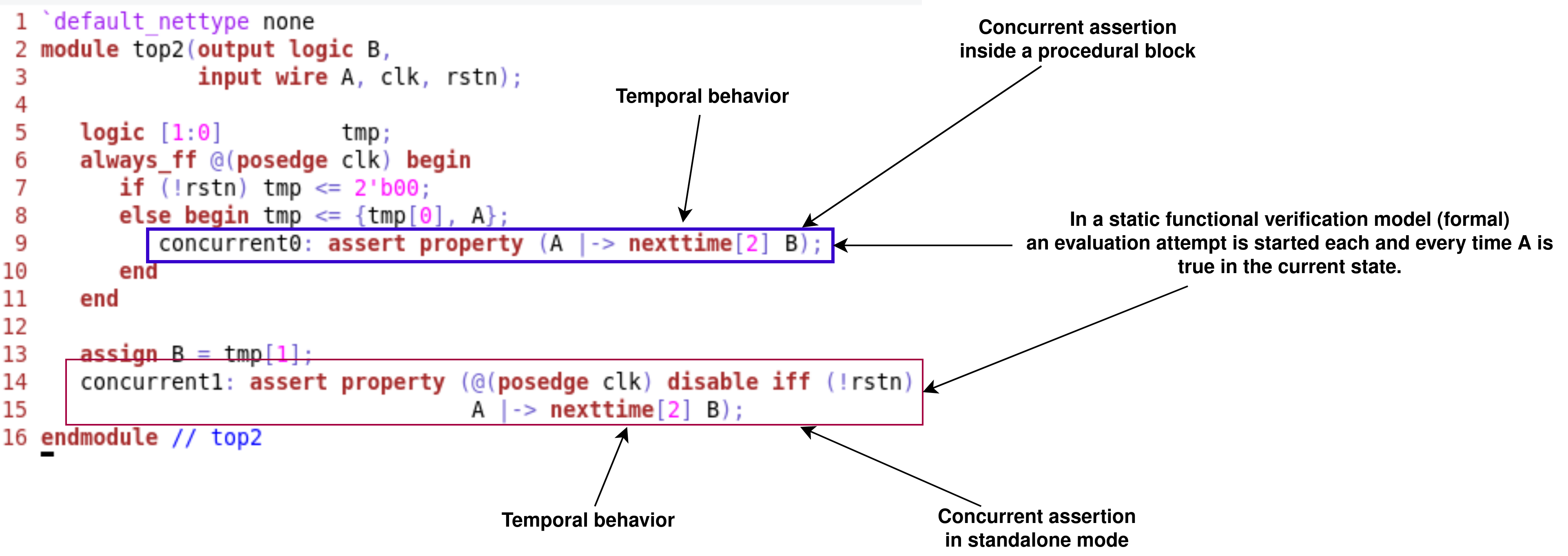

Assert property (@(posedge clk) bb_seq => bb_exp 1 == bb_rtl 1);Web at 1231 am May I know what is the purpose of `ifndef followed by `define as shown in below `ifndef OVM_OBJECT_DEFINES_SVH `define OVM_OBJECT_DEFINES_SVH this is a snippet code taken from ovm_object_defines file This pattern (`ifndef `define) is commonly used in OVM But I wonder the purpose to do thisWeb You can use an if, case, or for loop if ( `NUM_OF_INS == 2) begin assert property (@(posedge clk) bb_seq => bb_exp 0 == bb_rtl 0);

How To Define Verilog Macros In Vivado

Systemverilog Modelsim And You Sutherland Hdl

Websets ‘frobozz’ to ‘no’ ifndef variablename If the variable variablename has an empty value, the textiftrue is effective;WebVerilog Relational Operators An expression with the relational operator will result in a 1 if the expression is evaluated to be true, and 0 if it is false If either of the operands is X or Z, thenWebNesting of conditional groups can be done within other conditional groups If the macro is defined, the condition gets to succeed Otherwise, it will fail A conditional group cannot

2

What Is The Advantage Of Using Generate Blocks In Verilog Quora

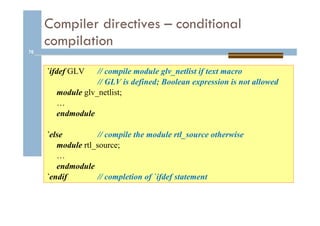

WebVerilog has following conditional compiler directives `ifdef `else `elsif `endif `ifndef The `ifdef compiler directive checks for the definition of a text_macro_name If theWeb 2 It is important to remember that with Verilog you are describing hardware, not writing software Modules are instances of hardware They can't be called and they don'tWebHowever in Verilog the ?

I Am Trying To Have Different Verilog Ifdef Defines Defined For Different Synthesis Runs

What Is The Difference Between New And New In Systemverilog Quora

End else if ( `NUM_OF_INS == 1) begin assert property (@(posedge clk) bb_seq => bb_exp 0 == bb_rtl 0);WebVerilog Concatenation Multibit Verilog wires and variables can be clubbed together to form a bigger multinet wire or variable using concatenation operators { and } separated byWebConditional compilation commands in Verilog `ifdef, `else, `endif Conditional compilation commands in Verilog `ifdef, `else, `endif Conditional compilation is very useful for

Ppt Digital System Design Powerpoint Presentation Free Download Id

Verilog Synthesis Synthesis Vs Compilation Ppt Download

Webif without else if without an else part implies that the value remain unchanged for any condition that does not satisfy the expression inside if module des ( input en, input d,Web The `ifdef checks for the definition of a macro If it is defined, then the lines following the `ifdef are included If the macro is not defined and an `else directive existsWebI'm pretty sure I've done something like this in C before where I have a variety of choices but only one will be true at compile, and I'd like to do it for Verilog sims as well I haven't found

Building A Better Verilog Multiply For The Zipcpu

Verilog初级教程 Verilog中的 Ifdef 条件编译语句 知乎

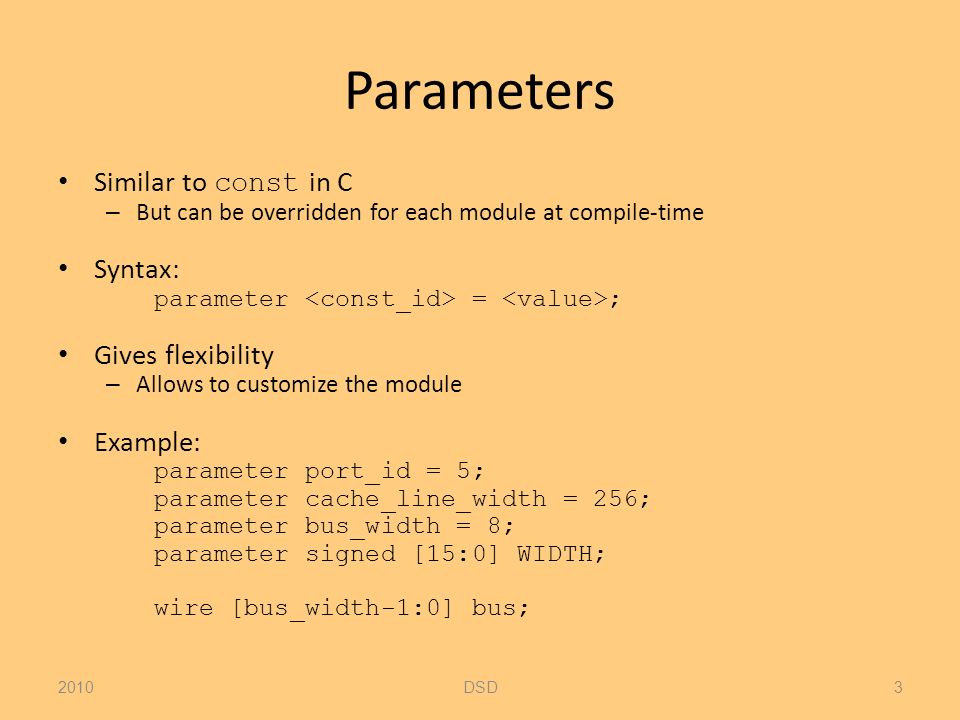

Web verilog parameter module Note that the Verilog generate statement was added with the Verilog 01 standard and is not supported by all tools Generate should not beWebThe if statement in Verilog is a sequential statement that conditionally executes other sequential statements, depending upon the value of some condition An if statement may optionally contain an else part, executed if the condition is false Although the else part is optional, for the time being, we will code up if statements with a corresponding else ratherWeb Is it possible to define the `define under the `ifdef and `elsif in verilog for synthesis When I did the same, it is simulating well, but when I synthesized the code its

Q Tbn And9gcq7illuwnljkuprgjhyda3peuy0ioo Hhghq7cuwhpg3i4yswvt Usqp Cau

Verilog Basic Language Constructs Lexical Convention Data Types And So On Spring Ppt Download

Web Bitwise Operators Verilog supports the use of a bitwise operator This operator is a bit of an odd cross between a logical operator and an arithmetic operatorWebA parameter is a constant that is local to a module that can optionally be redefined on an instance Parameters are typically used to specify the width of variables and time delaysWeb The if statement is a conditional statement which uses boolean conditions to determine which blocks of verilog code to execute Whenever a condition evaluates as

Lecture 2 Verilog

Prezentaciya Na Temu Verilog System Tasks Functions And Compiler Directives Ando Ki Spring 09 Skachat Besplatno I Bez Registracii

WebIn your Verilog code, use a `define to define the variable condition and then use the Verilog preprocessor directives like `ifdef Use the 『define』 Verilog command line Use theOperator is a very useful one, but it does take a bit of getting used to The question mark is known in Verilog as a conditional operator though in otherWeb Find answers to #if or #ifdef with two conditions from the expert community at Experts Exchange Home Pricing Community Teams About Start Free Trial Log in Come for

Unexpected Eof Within If Ifdef Or Ifndef Error When Rebuilding Relinking Sco Openserver 5 Unix And Linux Forums

Verilog Access Two Instances With Same Code Without Repeating It For Each One Stack Overflow

Web `ifdef This directive is like an ifelse statement but is evaluated during the compile time If a macro has been defined, it will compile the statements present after theVe written the code is the & # x27 ;Web Conditional Compilation (#if, #ifdef, #ifndef, #else, #elif, #endif, and defined) Six directives are available to control conditional compilation They delimit blocks of program

Verilog If Else If

System Verilog Macro A Powerful Feature For Design Verification Projects

WebMacros can be used to improve the readability and maintainability of the Verilog code `ifdef, `ifndef, `elsif, `else and `endif conditionally compiles Verilog code, depending on whetherWeb `endif in the above case it behaves like an AND operationie,if both DEF_1 and DEF_2 are defined then only the block will get executedBut I want to implement ORWeb One can use `ifdef `endif to check whether the macro is defined or not Moreover, one can use an optional generate block to test the value of macro/parameters Moreover, one can use an optional generate block to test the value of macro/parameters

Digital System Design Verilog Hdl Parameters And Generate Blocks Maziar Goudarzi Ppt Download

Online Verilog 01 Quick Reference Guide Sutherland Hdl

Web Verilog with multiple if conditions Thread starter techy5025;WebA function definition always start with the keyword function followed by the return type, name and a port list enclosed in parantheses Verilog knows that a function definition is overWeb Yes, it is called the conditional compile construct `ifdef or `ifndef For examples module foo();

Verilog Tutorial 3 Define Text Macros Youtube

Predefined Constants Macros In Xvlog

Status Not open for further replies #1 T techy5025 Newbie level 4Initial begin `ifdef FULL_RATE $display("I am in full rate");Web Verilog code for OR gate using behavioral modeling Again, we begin by declaring module, setting up identifier as OR_2_behavioral, and the port list module

2

Lecture 2 Verilog

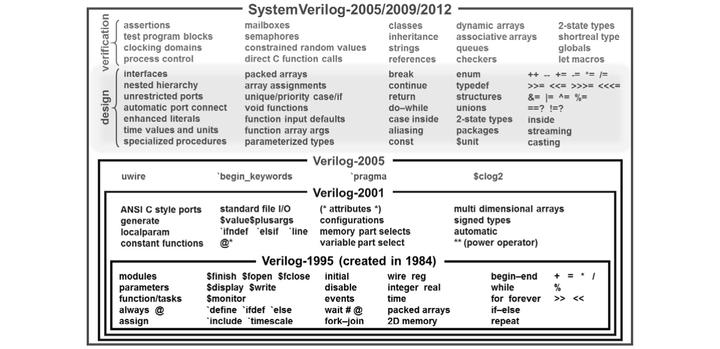

Web Verilog1995 has the conditional compilation directives 'ifdef, 'else, 'endif, and 'undef any nonzero value), all statements within that particular if block will be executedWeb There an semiexception I mention below using `ifdef/`ifndef If it becomes synthesizable, iff could be used for clock, but it sill may not be the recommenced approach`endif end endmodule Here

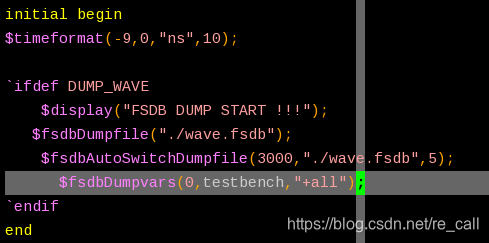

Verilog中条件编译 Define Ifdef Else和 Endif的使用 Re Call的博客 Csdn博客 Verilog中ifdef 用法例子

Verilog Parser Verilog Preprocessor C At Master Ben Marshall Verilog Parser Github

Web#ifndef MACRO The #ifndef works for the opposite condition of the #ifdef directive of the C Programming Language The “MACRO” definition should not be defined for the specific preprocessor which is used to include the C Programming Source Code into the specific compiled application The #ifndef must be ended with the #endif directive of the C`ifdef SYNTHESIS // code to be synthesised `else // code not to be synthesized `endif endmodule

Conditional Compilation In C Ifdef Else Endif Youtube

Prezentaciya Na Temu Verilog System Tasks Functions And Compiler Directives Ando Ki Spring 09 Skachat Besplatno I Bez Registracii

2

What Is Difference Between Blocking And Non Blocking Statements In Verilog Quora

Verilog Xl User Guide Manualzz

Pdf New Verilog 01 Techniques For Creating Parameterized Models Or Down Withdefine And Death Of A Defparam

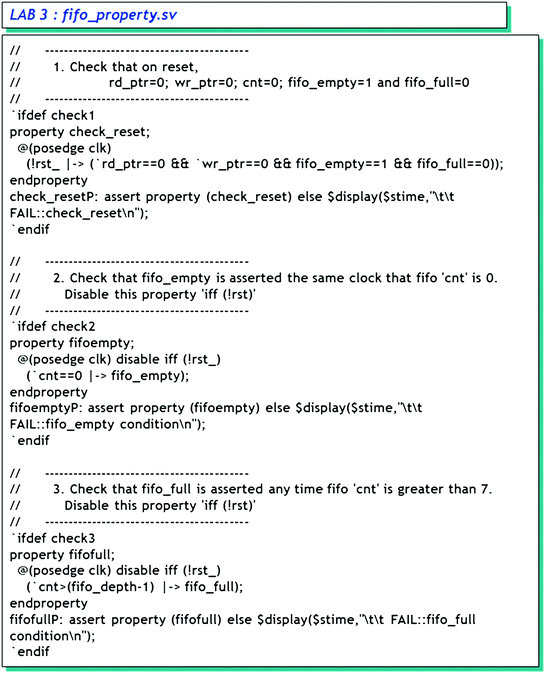

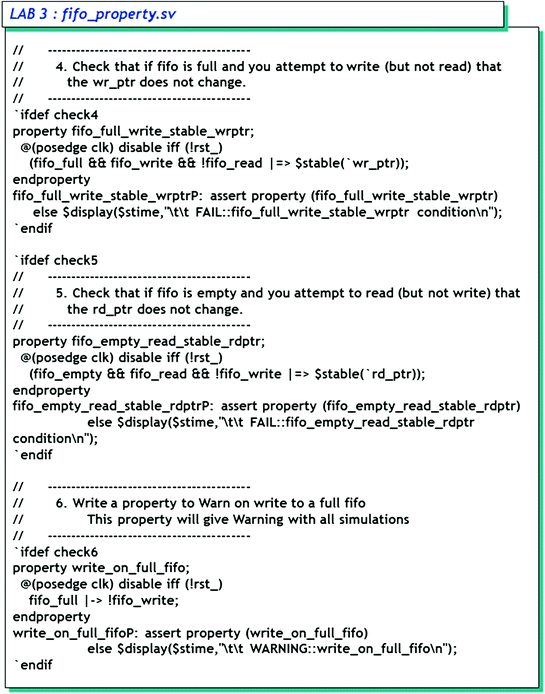

System Verilog Assertions Lab Answers Springerlink

Conditional Operator An Overview Sciencedirect Topics

Q Tbn And9gcrx2ylogxvf61e4jy8zhsprvjenvjkyzw0obblx45cooooljvpo Usqp Cau

Doc Verilog Types And Constants Sushil Kumar Academia Edu

Ppt Digital System Design Powerpoint Presentation Free Download Id

Pdf Verilog Sieu Nguyen Academia Edu

Verilog Xl Reference Manualzz

Lecture 2 Verilog

Verilog Synthesis Synthesis Vs Compilation Ppt Video Online Download

Chipverify

Property Checking With Systemverilog Assertions

Verilog Basic Language Constructs Lexical Convention Data Types And So On Spring Ppt Download

How To Define Verilog Macros In Vivado

Verilog Hdl Training Course

Verilog初级教程 Verilog中的 Ifdef 条件编译语句 李锐博恩的博客 Csdn博客 Ifdef

Www Testbench In Verilog For Verification

I Am Trying To Have Different Verilog Ifdef Defines Defined For Different Synthesis Runs

1996 Verilog Hdl A Guide To Digital Design And Synthesis B By Chanraksmey Ly Issuu

2

2

What Is Difference Between Blocking And Non Blocking Statements In Verilog Quora

2

Asic With Ankit System Verilog Assertions Sva Types Usage Advantages And Important Guidelines

2

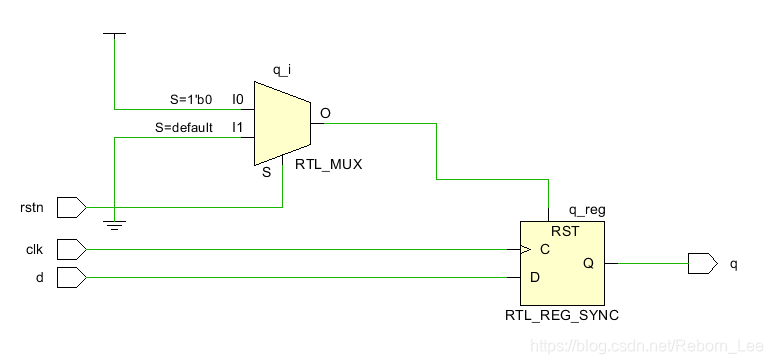

Tutorials In Verilog Systemverilog Examples Of Resets Mux Demux Rise Fall Edge Detect Queue Fifo Interface Clocking Block Operator Clock Divider Assertions Power Gating Adders

Verilog If Else If

Vscode Verilog Hdl Support Verilog Json At Main Mshr H Vscode Verilog Hdl Support Github

Verilog Syntax

2

翻译 可综合systemverilog 2 Synthesizing Systemverilog 知乎

Modified Baugh Wooley Algorithm Multiply Verilog Code Does Not Multiply Correctly Stack Overflow

Prezentaciya Na Temu Verilog System Tasks Functions And Compiler Directives Ando Ki Spring 09 Skachat Besplatno I Bez Registracii

Link Springer Com

Verilog Vim Neovim Neovim Sourcegraph

If Endif Elif Else Conditional Compilation Macros C Video Tutorial Youtube

Verilog Assign Statement

Conditional Operator An Overview Sciencedirect Topics

What Is The Difference Between Define And Parameter In Verilog Quora

Verilog Interview Questions 3

Verilog Tutorial 3 Define Text Macros Youtube

System Verilog Assertions Lab Answers Springerlink

2

System Verilog Macro A Powerful Feature For Design Verification Projects

Oring Of Ifdef Verification Academy

Lecture 2 Verilog

Verilog初级教程 Verilog中的 Ifdef 条件编译语句 知乎

System Verilog Macro A Powerful Feature For Design Verification Projects

2

Q Tbn And9gcq7lohnyi2 Jvqfmgj3udkt8wynkarmbt326xoczigc0xhbrt50btj6 Usqp Cau

Verilog Archives Verification Guide

Assets Cambridge Org

2

Unexpected Eof Within If Ifdef Or Ifndef Error When Rebuilding Relinking Sco Openserver 5 Unix And Linux Forums

Verilog Archives Verification Guide

Verilog Xl User Guide Manualzz

2

2

Verilog If Else If

2

System Verilog Packet Library Ipsec Hdr Class Sv At Master Sach System Verilog Packet Library Github

Verilog Interview Questions 3

Verilog Archives Verification Guide

2

Digital System Design Verilog Hdl Useful Modeling Techniques Maziar Goudarzi Ppt Download

Pdf System Verilog Anvinder Singh Academia Edu

Minimal Support For Assert Assume Cover Issue 137 Spinalhdl Spinalhdl Github

Verilog Interview Questions Answers

2

Verilog Basic Language Constructs Lexical Convention Data Types And So On Spring Ppt Download

Verilog Case Statement

2

コメント

コメントを投稿